SPARQ系列述评之二 ――信470uf 35v号完整性问题与S参数的干系

摘要:跟着半导体工艺的不绝成长,数字信号的速率也愈来愈高,Gbps以上的高速信号已经到处可见。面临高速设计的新规模,硬件设计工程师们需要改 变传统的设计理念,他们需要以越发超前的思维去思考本身将要设计的信号的质量,或者在拟定产物设计方案的时候就需要举办调研;需要在设计进程的每一个环节 去思考信号质量问题,如方案设计环节,道理图设计环节,PCB设计环节,测试验证环节等等;需要思量到系统中的每一个组成身分大概给信号质量带来的影响, 如过孔,电容,电感,阻抗,接插件等等;所有高速设计相关的问题也常被统称为信号完整性(即SI,Signal Integrity)问题,SI是当前硬件设计工程师们的一个最热门的话题之一。和SI相关的两个最为重要的事情是信号完整性仿真和信号完整性测试。信号 完整性仿真是指利用仿真软件将芯片、信号传输链路的模子毗连到一起,举办劈头的信号质量的预测,信号完整性仿真中一个最为重要的模子是S参数模子,它常被 用来模仿传输线、过孔、接插件等的模子,在仿真之初S参数经常是通过电磁场仿真软件等仿真的要领得到,然后再用相应的测试仪器如TDR、VNA以及力科新推出的新型专用于信号完整性规模的信号完整性网络阐明仪SPARQ等举办测试验证。S参数模子贯串于整个信号完整性阐明进程,它是一切信号完整性问题的心脏。

本文引用地点:要害词: 信号完整性 仿真 S参数 成立时间 保持时间

一、信号完整性的根基观念

SI(Signal Integrity)是指传输系统在信号的传输进程中保持信号的时域和频域特性的本领。

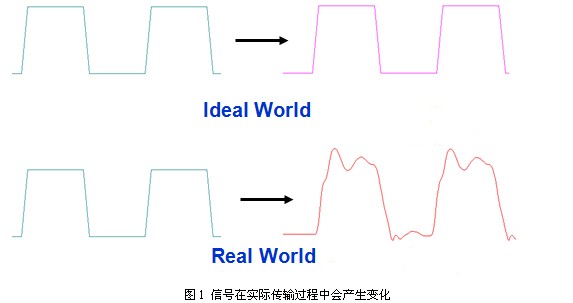

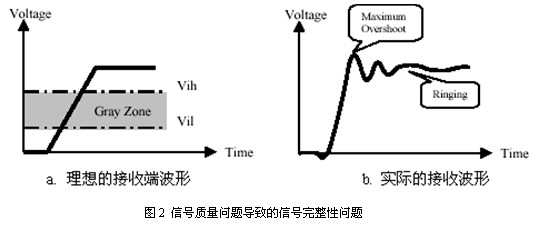

在抱负环境下,信号在传输进程中不该该产生任何的变革,可是真正抱负的传输通道是不存在的,实际环境是信号颠末一个非抱负的传输通道后会产生各 种百般的信号完整性问题。从信号质量角度思量,主要有过冲、下冲、振铃、反射等,信号质量问题会导致吸收端芯片错误的鉴别吸收到的信号的逻辑特性,如将0 电平误认为是1电平,从而呈现数据传输错误,别的一方面是时序问题,主要表示为数据和时钟之间的时序干系,如吸收端的时钟信号和数据信号不满意成立时间和 保持时间。

归纳综合来说,信号完整性问题主要表示为两个方面,一是信号质量问题;二是时序问题(主要是成立时间和保持时间)。

1、信号质量问题

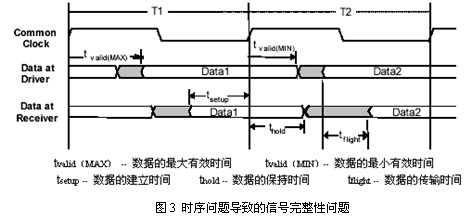

2、时序问题

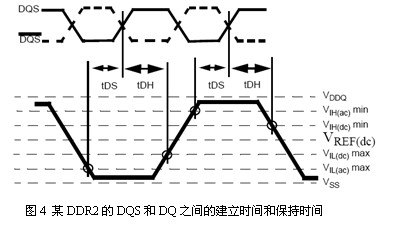

成立时间是指在时钟沿到来之前的一段时间内数据必需要保持有效状态(即高电平有效可能低电平有效),时钟沿和数据开始有效之间的这段时间即为成立时间值;保持时间是指在时钟沿之后数据还必需保持一段有效状态的时间,时钟沿和数据开始失效之间的时间即为保持时间值。

当前高机能示波器中都集成有成立时间和保持时间的专用丈量参数,如下图所示的Lecroy示波器中的成立时间和保持时间丈量示例。

二、如何办理信号完整性问题

当前信号完整性工程师面临信号完整性问题主要有两个要领,一是信号完整性仿真,二是信号完整性测试。测试的目标的一方面是验证系统最终的信号完整性机能,二是验证仿真功效的精确性。

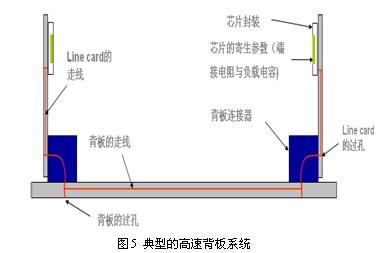

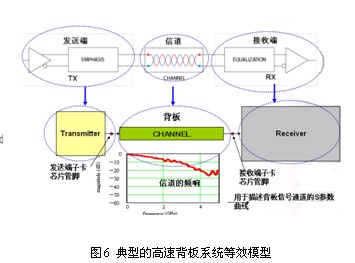

信号完整性仿真是在系统做成实物之前对整个系统举办仿真,系统中各个部门利用等效的电路模子,如下图5的高速背板系统可以等效为图6的模子。芯片利用厂家提供的HSPICE模子可能IBIS模子来等效,通道(包罗接插件、过孔、传输线等)凡是利用S参数模子来等效。

通道的S参数模子可以通过仿真软件提取获得,在完成实物今后, 220UF 10V,再利用测试要领举办S参数的测试验证以及系统整体机能的验证,如测试高速信号的眼图、发抖等。

由于硬件工程师无法改变芯片的模子,他们可以或许阐明研究的主要是整个链路的通道,而整个链路的通道响应特性可以由S参数来权衡。S参数可以回响通 道中各个构成身分的特性, 22UF 63V,如损耗、衰减、反射等。因此仿真中S参数的正确性将直接影响到仿真功效的正确性和可信性。因此,在系统完成后对S参数举办测试验 证长短常有须要的。

三、S参数可回响出所有的信号完整性问题

Copyright 2020© 东莞市立迈电子有限公司 版权所有 粤ICP备2020136922号-1

24小时服务电话:13336555866 邮箱:jimmy@limak.cn

公司地址:广东省东莞市塘厦镇东兴路162号振兴大厦 网站地图

在线客服①

在线客服①